# **CPC1001**

**CPU Module**

# **User Manual**

Rev. 001 October 2021

The product described in this manual is compliant with all related CE standards.

Product Title: CPC1001 Document name: CPC1001 User Manual User Manual version: 001 Ref. docs:

Copyright © 2021 Fastwel Co. Ltd. All rights reserved.

#### **Revision Record**

| Rev. Index | Brief Description   | Product Index | Date          |

|------------|---------------------|---------------|---------------|

| 001        | Preliminary version | CPC1001       | October, 2021 |

|            |                     |               |               |

|            |                     |               |               |

#### **Contact Information**

|          | Fastwel Co. Ltd                                                |         | Fastwel Corporation US                                      |

|----------|----------------------------------------------------------------|---------|-------------------------------------------------------------|

| Address: | 108 Profsoyuznaya St.,<br>Moscow 117437,<br>Russian Federation |         | 6108 Avenida Encinas,<br>Suite B, Carlsbad,<br>CA92011, USA |

| Tel.:    | +7 (495) 232-1681                                              | Tel.:   | +1 (858) 488-3663                                           |

| Fax:     | +7 (495) 232-1654                                              |         |                                                             |

| E-mail:  | info@fastwel.com                                               | E-mail: | info@fastwel.com                                            |

| Web:     | http://www.fastwel.com/                                        |         |                                                             |

# **Table of Contents**

|     | Table of (     | Contents                                                                                                       | 1  |

|-----|----------------|----------------------------------------------------------------------------------------------------------------|----|

|     | List of Ta     | bles                                                                                                           | 2  |

|     | List of Fig    | gures                                                                                                          | 3  |

|     | Conventio      | ons                                                                                                            | 5  |

|     | Manufact       | turer's warranties                                                                                             | 6  |

|     | Transport      | tation, Unpacking and Storage                                                                                  | 8  |

| 1   | Descrip        | tion and operation                                                                                             | 10 |

|     | 1.1            | Purpose of the device                                                                                          | 10 |

|     | 1.2            | Technical specifications                                                                                       | 10 |

|     | 1.3            | Overview                                                                                                       | 13 |

|     | 1.4            | Dimensions and weight                                                                                          | 13 |

|     | 1.5            | Ordering information on CPC1001                                                                                | 13 |

|     | 1.6            | Structure and operation                                                                                        | 14 |

|     | 1.6.1          | Location of CPC1001 elements                                                                                   |    |

|     | 1.6.2<br>1.6.3 | SMARC connector of the CPC1001 module<br>Compliance of the SMARC interfaces and interface controllers of i.MX6 |    |

|     | 1.6.4          | Arrangement of 16-bit parallel bus.                                                                            |    |

|     | 1.7            | Delivery checklist                                                                                             | 22 |

|     | 1.8            | Packaging                                                                                                      | 23 |

|     | 1.8.1          | Size of the consumer container and weight of the packaged product                                              |    |

|     | 1.8.2<br>1.8.3 |                                                                                                                |    |

| _   |                |                                                                                                                |    |

| 2   | Intende        | d Use                                                                                                          |    |

|     | 2.1 Opera      | ating limitations                                                                                              | 24 |

|     |                | y requirements                                                                                                 |    |

|     |                | nation on the types of hazardous effects                                                                       |    |

|     |                | removal                                                                                                        |    |

|     |                | llation of CPC1001                                                                                             |    |

|     |                | ction of OS boot source                                                                                        |    |

|     |                | er up and down                                                                                                 |    |

|     | 2.8 Remo       | oval of CPC1001                                                                                                |    |

| 3   | Mainten        | nance and repairs                                                                                              | 32 |

|     | 3.1 Maint      | tenance                                                                                                        | 32 |

|     | 3.2 Repa       | irs                                                                                                            | 32 |

|     |                | CLAIMER                                                                                                        | 00 |

| ANT |                |                                                                                                                |    |

1

# List of Tables

| Table 1-1: | Purpose of pins of the SMARC connector of CPC1001                    | 15 |

|------------|----------------------------------------------------------------------|----|

| Table 1-2: | Compliance of the SMARC interfaces and i.MX6 processor               | 21 |

| Table 1-3: | Signals of parallel bus                                              | 22 |

| Table 2-1: | Recommended components for CPC1001 installation to the carrier-board | 27 |

| Table 2-2: | Boot sources of CPC1001                                              | 29 |

| Table 2-3: | Requirements to the supply voltages of CPC1001                       |    |

| Table 2-4: | Dependency of critical output signals                                | 31 |

#### **List of Figures**

| Figure 1-1: | CPC1001-02                                   | 13  |

|-------------|----------------------------------------------|-----|

| Figure 2-1: | Removal of the shipping screws on CPC1001-01 | .27 |

| Figure 2-2: | Mounting dimensions of CPC1001-01            | .28 |

All information in this document is provided for reference only, with no warranty of its suitability for any specific purpose. This information has been thoroughly checked and is believed to be entirely reliable and consistent with the product that it describes. However, Fastwel accepts no responsibility for inaccuracies, omissions or their consequences, as well as liability arising from the use or application of any product or example described in this document.

Fastwel Co. Ltd. reserves the right to change, modify, and improve this document or the products described in it, at Fastwel's discretion without further notice. Software described in this document is provided on an "as is" basis without warranty. Fastwel assumes no liability for consequential or incidental damages originated by the use of this software.

This document contains information, which is property of Fastwel Co. Ltd. It is not allowed to reproduce it or transmit by any means, to translate the document or to convert it to any electronic form in full or in parts without antecedent written approval of Fastwel Co. Ltd. or one of its officially authorized agents.

Fastwel and Fastwel logo are trademarks owned by Fastwel Co. Ltd., Moscow, Russian Federation. CompactPCI is a trademark of the PCI industrial Computers Manufacturers Group. Ethernet is a registered trademark of Xerox Corporation. IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc. Intel is a trademark of Intel Corporation. Pentium M and Celeron M are trademarks of Intel Corporation. Microsoft is a trademark of the Microsoft Corporation. In addition, this document may include names, company logos and trademarks, which are registered trademarks and, therefore, are property of their respective owners. Fastwel welcomes suggestions, remarks and proposals regarding the form and the content of this Manual.

#### **Ownership rights**

This document contains information that is the property of Fastwel Group. It may not be copied or transmitted by any known means, nor may it be stored in information storage and retrieval systems without the prior written consent of Fastwel Group or one of its authorized agents. The information contained in this document, to the best of our knowledge, is free from any errors, however, Fastwel Group accepts no responsibility for any inaccuracies and their consequences, as well as liability arising from the use or application of any diagram, product or example given in this document. Fastwel Group reserves the right to change and improve both this document and the product presented inside of it at its discretion without any further notice.

### Safety requirements

This Fastwel Group's product is developed and tested for the purpose of ensuring compliance to the electric safety requirements. Its design provides long-term trouble-free operation. The service life of the product can be significantly reduced due to the improper handling during unpacking and installation. Therefore, in the interests of your safety and in order to ensure proper operation of the product, you should follow the recommendations below.

# Conventions

This sign and text warn of the dangers associated with electrical discharges (> 60 V) when touching the device or any part of it. Failure to follow the precautions mentioned or prescribed in the regulations may endanger your life or health, and may result in damages to the equipment. Please also read the below subparagraph dedicated to the rules for working with high voltage.

#### Attention! Static-sensitive device!

This sign and text indicate that electronic boards and their components are sensitive to static electricity, so care should be taken when handling this device and performing inspections to ensure integrity and functionality of the device.

#### Attention! Hot surface!

This sign and text warn of the danger associated with touching hot surfaces of the device.

This sign is aimed at drawing your attention to aspects of this User Manual that, if not fully understood or ignored, may endanger your health or cause damages to the equipment.

This sign is used to text fragments that should be read carefully.

This User Manual (hereinafter referred to as the User Manual or UM) covers the CPC1001 CPU Module and contains description, operating principle and technical specifications of CPC1001, as well as establishes the rules and procedures for its operation.

Carefully read this User Manual before using the product.

The manufacturer is not responsible for any possible damages and breakdowns caused by noncompliance with the recommendations and requirements of this User Manual.

All operations with this device should only be performed by personnel with sufficient qualifications.

## **MANUFACTURER'S WARRANTIES**

#### Warranty liabilities

The manufacturer guarantees that CPC1001 meets the requirements of technical specifications of the "CPU MODULE IN SMARC (Smart Mobility ARChitecture) FORMAT" IMES.467444.111 TU provided that the Consumer complies with the operating conditions, transportation, storage, installation and mounting, set by the operational documents.

The manufacturer guarantees that the products supplied by it will not show any manufacturing defects and the materials used comply with the rules of operation and maintenance during the warranty period established at the moment. The Manufacturer's obligation under this warranty is to repair or replace, free of charge, any defective electronic component included in the returned product.

Products that failed through the Manufacturer's fault during the warranty period will be repaired free of charge. In other cases, the Consumer will be billed based on current remuneration rates and the cost of consumables.

#### **Right of limitation liability**

The manufacturer is not responsible for any damages caused to the Consumer's property due to the failure of the product in the process of its use.

#### Warranty period

The warranty period for the manufacturer's products is 36 months from the date of sale (unless otherwise provided by the delivery agreement).

For customized products, the warranty period is 60 months from the date of sale (unless otherwise provided by the delivery agreement).

#### The warranty set forth above does not extend to and shall not apply to:

- Products, including software, which have been repaired or altered by other than Fastwel personnel, unless Buyer has properly altered or repaired the products in accordance with procedures previously approved in writing by Fastwel.

- 2. Products, which have been subject to power supply reversal, misuse, neglect, accident, or improper installation.

#### Returning a product for repair

- 1. Apply to Fastwel Company or to any of the Fastwel's official representatives for the Product Return Authorization.

- 2. Attach a failure inspection report with a product to be returned in the form, accepted by customer, with a description of the failure circumstances and symptoms.

- Carefully package the product in the antistatic bag, in which the product had been supplied. Failure to package in antistatic material will VOID all warranties. Then package the product in a safe container for shipping.

- 4. The customer pays for shipping the product to Fastwel or to an official Fastwel representative or dealer.

# Transportation, Unpacking and Storage

# Transportation

The modules should be transported in the separate manufacturer's packaging (container), consisting of an individual antistatic packaging and a cardboard box.

The packaging should ensure the integrity and performance of the product after transportation.

Attention!

During transportation, the transport packaging should provide proper protection of the product against direct exposure of atmospheric precipitation.

#### Hauling equipment and climatic conditions

The modules should be transported in closed transport (by road, rail or air in heated and sealed compartments) under storage conditions 5 in accordance with the GOST 15150-69 standard or under storage conditions 3 for sea transportation.

#### Placement and fastening of shipping containers

The shipping containers should be placed and fastened in such a way that will ensure their stable position, exclude their displacement and damages by impacts during transportation.

#### Attention!

During handling operations and transportation, the packed modules should not be subjected to sudden shocks, drops or impacts, which may affect their safety and performance.

# Storage

Storage conditions of the modules 1 comply with the GOST standard 15150-69.

# Unpacking

#### Safety precautions

Before unpacking, after transportation at negative ambient temperatures, the modules must be kept for 6 hours under storage conditions 1, in accordance with the GOST standard 15150-69.

Do not place the packaged modules near any heat sources before unpacking.

When unpacking the modules, it is necessary to observe all precautions to ensure their safety, as well as marketable condition of manufacturer's consumer packaging.

#### Assessment of exterior appearance

When unpacking, it is necessary to check the modules for any external mechanical damages after transportation.

If during unpacking you discover that the CPC1001 module has any external mechanical damages or any component from the delivery set (subsection 1.7) is missing, please contact the official distributor from which this product was purchased.

Please retain the product's consumer packaging (box) and antistatic packaging in their original form until the end of the warranty period.

# **1** Description and operation

## 1.1 Purpose of the device

Device name: CPC1001 CPU Module.

Product identification: IMES.467444.131.

The CPC1001 processor module (hereinafter referred to as the CPC1001 module or simply as CPC1001) is designed for the use as a high-performance computing core with a wide range of I/O interfaces when building real-time control systems for critical applications with strict requirements for dimensions, power consumption and operating conditions.

### 1.2 Technical specifications

- 1.2.1 SMARC form-factor, version 1.1:

- size (without heatsink) 82.0 × 50.0 × 4.9 mm;

- size (with heatsink) 82.0  $\times$  50.0  $\times$  8.8 mm;

- weight (without heatsink) 20 g;

- weight (with heatsink) 60 g.

- 1.2.2 Processor i.MX 6Quad (0.8-1.0 GHz):

- 4 Out-of-Order Execution processor cores;

- L1-Cache (32 kB Instructions, 32 kB Data);

- L2-Cache 1024 kB;

- Cortex-A9 NEON MPE (Media Processing Engine) Co-processor;

- Internal multimedia / shared, fast access RAM (OCRAM, 512 kB) Intel Digital Random

Number Generator;

- Secure/non-secure RAM (16 kB);

- External memory interfaces.

- 1.2.3 RAM:

- DDR3L-1066 SDRAM 4 GB;

- 64-bit data bus.

- 1.2.4 Flash memory:

- eMMC Flash disk 32 GB;

- SPI-Flash 4 MB;

- I2C-Flash 4 kB.

- 1.2.5 Connector MXM 3.0:

- 1 x port PCIe x1 (PCIe Base Spec. Rev 2.0), 5 GT/s;

- 1 x port USB 2.0 (host);

- 1 x port USB OTG 2.0;

- 1 x port SATA II (3-Gbps Gen. II);

- 1 x port Gbit Ethernet;

- 2 x SPI ports;

- Port "LVDS Channel A": LVDS;

- Port "HDMI 1.4 HD1080 @ 50Hz;

- 2 x CAN ports;

- 3 x I2C ports;

- 2 x I2S ports;

- SDIO port (combined with GPIO ports);

- 3 x UART ports (LVCMOS, 64-byte FIFO, up to 4 Mbps);

- port MMC 8-bit;

- "RTC battery" port.

- 1.2.6 Operating system (hereinafter referred to as the OS) boot interfaces:

- selection from eight alternative sources using three configuration inputs;

- 1.2.7 Watchdog timer: integrated into the processor interval from 1 µs to 10 min;

- 1.2.8 Real Time Clock (power is supplied from the "RTC battery" port);

- 1.2.9 Software compatibility:

- Linux;

- Android.

#### 1.2.10 Power supply:

- from 3.3 to 5.25 V for the version CPC1001-01;

- from 3.3 to 4.5 V for the version CPC1001-02;

- power consumption:

- extreme loading scenario up to 9 W<sup>1</sup>;

- realistic scenario of heavy load up to 5 W;

- sleep mode about 100 mW.

1.2.11 Environmental characteristics:

- operating temperature range from -40 to +85 °C;

- exposure of sinusoidal vibration of 5g for the frequencies ranging from 10 to 500 Hz;

- exposure of multiple shocks 50g and single shocks 100g.

1.2.12 Electromagnetic compatibility:

CPC1001 is resistant to electromagnetic interference in accordance with the requirements of the GOST CISPR 24;

level of radio interference caused during operation of CPC1001 does not exceed the values set by the GOST standard 30805.22-2013 for class A production units.

1.2.13 MTBF – 450,000 hours.

The MTBF value is calculated using the Telcordia Issue 1 calculation model (Method I Case 3) for continuous operation when located on the ground under conditions corresponding to the climatic category Moderately Cold Climate 4 in accordance with GOST 15150-69 standard, at an ambient temperature of +30°C.

<sup>&</sup>lt;sup>1</sup>The scenario corresponds to the artificially generated, atypical, extremely heavy use of memory, video, SD and GBE.

### 1.3 Overview

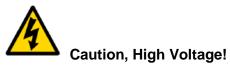

Fig.1.1 shows the overview of CPC1001-02.

Fig. 1.1 - CPC1001-02

### 1.4 Dimensions and weight

Dimensions of CPC1001 are as follows:

- CPC1001-01 max. 82.0 × 50.0 × 8.8 mm;

- CPC1001-02 max. 82.0 × 50.0 × 4.9 mm.

Weight of CPC1001:

- CPC1001-01 max. 0.06 kg;

- CPC1001-02 max. 0.02 kg.

# 1.5 Ordering information on CPC1001

The manufacturer produces CPC1001 modules with the following design:

- CPC1001-01 IMES.467444.131 - with a power supply voltage ranging from 3.3 to 5.25 V, with an installed heatsink;

- CPC1001-02 IMES.467444.131-01 - with a power supply voltage ranging from 3.3 to 4.5 V, without a heatsink (Fig.1.1).

The CPC1001-02 module is 10-15% more efficient in terms of power consumption, but its consumption along the power supply circuit of the real-time clock is rather high - about 60  $\mu$ A, which makes it impractical to use the batteries of 2032 type. When it comes to the CPC1001-01 version, the consumption along the power supply circuit of the real-time clock is about 1  $\mu$ A (for more details see subparagraph 2.7 *Power up and down*).

## **1.6 Structure and operation**

#### 1.6.1 Location of CPC1001 elements

Example of how the CPC1001 elements are located is demonstrated with the CPC1001-01 version in Fig. 1.2. The heatsink is used to remove heat from the microchips installed on the CPC1001-01 board (for more details on heat removal, see subparagraph 2.4). I/O interfaces of the SMARC connector are listed in paragraph 1.2. The purpose of pins of the SMARC connector is shown in table. 1.1.

Fig. 1.2 – Structural elements of CPC1001-01

#### 1.6.2 SMARC connector of the CPC1001 module

The SMARC connector is used when installing the module on a carrier board (subparagraph 2.5). The purpose of the SMARC connector pins of CPC1001 is given in table 1.1.

Tab. 1.1 - Purpose of the SMARC connector pins of the CPC1001 module

#### Table 1.1 – Purpose of pins of the SMARC connector of CPC1001

| TOP pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor              | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor            |

|---------|-------------------------------------------|----------------------------------------|---------------|-------------------------------------------|--------------------------------------|

|         |                                           | -                                      | S1            | PCAM_VSYNC                                | CSI0_VSYNC<br>ALT0 IPU1_CSI0_VSYNC   |

| P1      | PCAM_PXL_CK1                              | Not connected                          | S2            | PCAM_HSYNC                                | CSI0_MCLK<br>ALT0 IPU1_CSI0_HSYNC    |

| P2      | GND                                       | -                                      | S3            | GND                                       | -                                    |

| P3      | CSI1_CK+/<br>PCAM_D0                      | CSI0_DAT12<br>ALT0 IPU1_CSI0_DATA12    | S4            | PCAM_PXL_CK0                              | CSI0_PIXCLK<br>ALT0 IPU1_CSI0_PIXCLK |

| P4      | CSI1_CK-<br>/PCAM_D1                      | CSI0_DAT13<br>ALT0 IPU1_CSI0_DATA13    | S5            | I2C_CAM_CK                                | KEY_COL3<br>ALT4 I2C2_SCL            |

| P5      | PCAM_DE                                   | CSI0_DATA_EN<br>ALT0 IPU1_CSI0_DATA_EN | S6            | CAM_MCK                                   | GPIO_19<br>ALT3 CCM_CLKO1            |

| P6      | PCAM_MCK                                  | -                                      | S7            | I2C_CAM_DAT                               | KEY_ROW3<br>ALT4 I2C2_SDA            |

| P7      | CSI1_D0+/<br>PCAM_D2                      | CSI0_DAT14<br>ALT0 IPU1_CSI0_DATA14    | S8            | CSI0_CK+/<br>PCAM_D10                     | CSI_CLK0P                            |

| P8      | CSI1_D0-<br>/PCAM_D3                      | CSI0_DAT15<br>ALT0 IPU1_CSI0_DATA15    | S9            | CSI0_CK-<br>/PCAM_D11                     | CSI_CLK0M                            |

| P9      | GND                                       | -                                      | S10           | GND                                       | -                                    |

| P10     | CSI1_D1+/<br>PCAM_D4                      | CSI0_DAT16<br>ALT0 IPU1_CSI0_DATA16    | S11           | CSI0_D0+/<br>PCAM_D12                     | CSI_D0P                              |

| P11     | CSI1_D1-<br>/PCAM_D5                      | CSI0_DAT17<br>ALT0 IPU1_CSI0_DATA17    | S12           | CSI0_D0-<br>/PCAM_D13                     | CSI_D0M                              |

| P12     | GND                                       | -                                      | S13           | GND                                       | -                                    |

| P13     | CSI1_D2+/<br>PCAM_D6                      | CSI0_DAT18<br>ALT0 IPU1_CSI0_DATA18    | S14           | CSI0_D1+/<br>PCAM_D14                     | CSI_D1P                              |

| P14     | CSI1_D2-<br>/PCAM_D7                      | CSI0_DAT19<br>ALT0 IPU1_CSI0_DATA19    | S15           | CSI0_D1-<br>/PCAM_D15                     | CSI_D1M                              |

| P15     | GND                                       | -                                      | S16           | GND                                       | -                                    |

| P16     | CSI1_D3+/<br>PCAM_D8                      | Not connected                          | S17           | AFB0_OUT                                  | EIM_BCLK<br>ALT5 GPIO6_IO31          |

| P17     | CSI1_D3-<br>/PCAM_D9                      | Not connected                          | S18           | AFB1_OUT                                  | EIM_WAIT<br>ALT5 GPIO5_IO00          |

| P18     | GND                                       | -                                      | S19           | AFB2_OUT                                  | EIM_EB0<br>ALT5 GPIO2_IO28           |

| P19     | GBE_MDI3-                                 | GBE_PHY TXRXM_D                        | S20           | AFB3_IN                                   | EIM_EB1<br>ALT5 GPIO2_IO29           |

| P20     | GBE_MDI3+                                 | GBE_PHY TXRXP_D                        | S21           | AFB4_IN                                   | EIM_AD00<br>ALT5 GPIO3_IO00          |

| P21     | GBE_LINK100#                              | GBE_PHY LED1                           | S22           | AFB5_IN                                   | EIM_AD01<br>ALT5 GPIO3_IO01          |

| P22     | GBE_LINK1000#                             | GBE_PHY LED2                           | S23           | AFB6_PTIO                                 | EIM_AD02<br>ALT5 GPIO3_IO02          |

| P23     | GBE_MDI2-                                 | GBE_PHY TXRXM_C                        | S24           | AFB7_PTIO                                 | EIM_AD03<br>ALT5 GPIO3_IO03          |

| P24     | GBE_MDI2+                                 | GBE_PHY TXRXP_C                        | S25           | GND                                       | -                                    |

| P25     | GBE_LINK_ACT#                             | Not connected                          | S26           | SDMMC_D0                                  | SD3_DAT0<br>ALT0 SD3_DATA0           |

| TOP<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                        | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor   |

|------------|-------------------------------------------|--------------------------------------------------|---------------|-------------------------------------------|-----------------------------|

| P26        | GBE_MDI1-                                 | GBE_PHY TXRXM_B                                  | S27           | SDMMC_D1                                  | SD3_DAT1<br>ALT0 SD3_DATA1  |

| P27        | GBE_MDI1+                                 | GBE_PHY TXRXP_B                                  | S28           | SDMMC_D2                                  | SD3_DAT2<br>ALT0 SD3_DATA2  |

| P28        | GBE_CTREF                                 | Not connected                                    | S29           | SDMMC_D3                                  | SD3_DAT3<br>ALT0 SD3_DATA3  |

| P29        | GBE_MDI0-                                 | GBE_PHY TXRXM_A                                  | S30           | SDMMC_D4                                  | SD3_DAT4<br>ALT0 SD3_DATA4  |

| P30        | GBE_MDI0+                                 | GBE_PHY TXRXP_A                                  | S31           | SDMMC_D5                                  | SD3_DAT5<br>ALT0 SD3_DATA5  |

| P31        | SPI0_CS1#                                 | EIM_D19<br>ALT1 ECSPI1_SS1 or<br>ALT5 GPIO3_IO19 | S32           | SDMMC_D6                                  | SD3_DAT6<br>ALT0 SD3_DATA6  |

| P32        | GND                                       | -                                                | S33           | SDMMC_D7                                  | SD3_DAT7<br>ALT0 SD3_DATA7  |

| P33        | SDIO_WP                                   | GPIO_2<br>ALT6 SD2_WP or<br>ALT5 GPIO1_IO02      | S34           | GND                                       | -                           |

| P34        | SDIO_CMD                                  | SD2_CMD<br>ALT0 SD2_CMD                          | S35           | SDMMC_CK                                  | SD3_CLK<br>ALT0 SD3_CLK     |

| P35        | SDIO_CD#                                  | GPIO_4<br>ALT6 SD2_CD_B or<br>ALT5 GPIO1_IO04    | S36           | SDMMC_CMD                                 | SD3_CMD<br>ALT0 SD3_CMD     |

| P36        | SDIO_CK                                   | SD2_CLK<br>ALT0 SD2_CLK                          | S37           | SDMMC_RST#                                | SD3_RST<br>ALT0 SD3_RESET   |

| P37        | SDIO_PWR_EN                               | GPIO_5<br>ALT5 GPIO1_IO05                        | S38           | AUDIO_MCK                                 | GPIO_19<br>ALT3 CCM_CLKO1   |

| P38        | GND                                       | -                                                | S39           | I2S0_LRCK                                 | CSI0_DAT6<br>ALT4 AUD3_TXFS |

| P39        | SDIO_D0                                   | SD2_DAT0<br>ALT0 SD2_DATA0                       | S40           | I2S0_SDOUT                                | CSI0_DAT5<br>ALT4 AUD3_TXD  |

| P40        | SDIO_D1                                   | SD2_DAT1<br>ALT0 SD2_DATA1                       | S41           | I2S0_SDIN                                 | CSI0_DAT7<br>ALT4 AUD3_RXD  |

| P41        | SDIO_D2                                   | SD2_DAT2<br>ALT0 SD2_DATA2                       | S42           | I2S0_CK                                   | CSI0_DAT4<br>ALT4 AUD3_TXC  |

| P42        | SDIO_D3                                   | SD2_DAT3<br>ALT0 SD2_DATA3                       | S43           | I2S1_LRCK                                 | KEY_COL1<br>ALT2 AUD5_TXFS  |

| P43        | SPI0_CS0#                                 | Not connected                                    | S44           | I2S1_SDOUT                                | KEY_ROW0<br>ALT2 AUD5_TXD   |

| P44        | SPI0_CK                                   | EIM_D16<br>ALT1 ECSPI1_SCLK                      | S45           | I2S1_SDIN                                 | KEY_ROW1<br>ALT2 AUD5_RXD   |

| P45        | SPI0_DIN                                  | EIM_D17<br>ALT1 ECSPI1_MISO                      | S46           | I2S1_CK                                   | KEY_COL0<br>ALT2 AUD5_TXC   |

| P46        | SPI0_DO                                   | EIM_D18<br>ALT1 ECSPI1_MOSI                      | S47           | GND                                       | -                           |

| P47        | GND                                       | -                                                | S48           | I2C_GP_CK                                 | GPIO_3<br>ALT2 I2C3_SCL     |

| P48        | SATA_TX+                                  | SATA_TXP                                         | S49           | I2C_GP_DAT                                | GPIO_6<br>ALT2 I2C3_SDA     |

| P49        | SATA_TX-                                  | SATA_TXM                                         | S50           | I2S2_LRCK                                 | Not connected               |

| P50        | GND                                       | -                                                | S51           | I2S2_SDOUT                                | Not connected               |

| P51        | SATA_RX+                                  | SATA_RXP                                         | S52           | I2S2_SDIN                                 | Not connected               |

| P52        | SATA_RX-                                  | SATA_RXM                                         | S53           | I2S2_CK                                   | Not connected               |

| P53        | GND                                       | -                                                | S54           | SATA_ACT#                                 | GPIO_17<br>ALT5 GPIO7_IO12  |

| TOP<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                                                                             | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor   |

|------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------|-----------------------------|

| P54        | SPI1_CS0#                                 | EIM_RW<br>ALT2 ECSPI2_SS0 or ALT5<br>GPIO2_IO26                                                       | S55           | AFB8_PTIO                                 | EIM_AD08<br>ALT5 GPIO3_IO08 |

| P55        | SPI1_CS1#                                 | EIM_LBA<br>ALT2 ECSPI2_SS1 or<br>ALT5 GPIO2_IO27                                                      | S56           | AFB9_PTIO                                 | EIM_AD09<br>ALT5 GPIO3_IO09 |

| P56        | SPI1_CK                                   | EIM_CS0<br>ALT2 ECSPI2_SCLK                                                                           | S57           | PCAM_ON_CSI0#                             | Not connected               |

| P57        | SPI1_DIN                                  | EIM_OE<br>ALT2 ECSPI2_MISO                                                                            | S58           | PCAM_ON_CSI1#                             | GND                         |

| P58        | SPI1_DO                                   | EIM_CS1<br>ALT2 ECSPI2_MOSI                                                                           | S59           | SPDIF_OUT                                 | ENET_RXD0<br>ALT3 SPDIF_OUT |

| P59        | GND                                       | -                                                                                                     | S60           | SPDIF_IN                                  | ENET_RX_ER ALT3<br>SPDIF_IN |

| P60        | USB0+                                     | USB_OTG_DP                                                                                            | S61           | GND                                       | -                           |

| P61        | USB0-                                     | USB_OTG_DM                                                                                            | S62           | AFB_DIFF0+                                | EIM_AD06<br>ALT5 GPIO3_IO06 |

| P62        | USB0_EN_OC#                               | EIM_D22<br>ALT4 USB_OTG_PWR or<br>ALT5 GPIO3_IO22<br>EIM_D21<br>ALT4 USB_OTG_OC or<br>ALT5 GPIO3_IO21 | S63           | AFB_DIFF0-                                | EIM_AD07<br>ALT5 GPIO3_IO07 |

| P63        | USB0_VBUS_DET                             | USB_OTG_VBUS                                                                                          | S64           | GND                                       | -                           |

| P64        | USB0_OTG_ID                               | GPIO_1<br>ALT3 USB_OTG_ID or<br>ALT5 GPIO1_IO01                                                       | S65           | AFB_DIFF1+                                | EIM_AD08<br>ALT5 GPIO3_IO08 |

| P65        | USB1+                                     | USB_H1_DP                                                                                             | S66           | AFB_DIFF1-                                | EIM_AD09<br>ALT5 GPIO3_IO09 |

| P66        | USB1-                                     | USB_H1_DN                                                                                             | S67           | GND                                       | -                           |

| P67        | USB1_EN_OC#                               | EIM_D31<br>ALT6 USB_H1_PWR or<br>ALT5 GPIO3_IO31<br>EIM_D30<br>ALT6 USB_H1_OC or<br>ALT5 GPIO3_IO30   | S68           | AFB_DIFF2+                                | EIM_AD10<br>ALT5 GPIO3_IO10 |

| P68        | GND                                       | -                                                                                                     | S69           | AFB_DIFF2-                                | EIM_AD11<br>ALT5 GPIO3_IO11 |

| P69        | USB2+                                     | Not connected                                                                                         | S70           | GND                                       | -                           |

| P70        | USB2-                                     | Not connected                                                                                         | S71           | AFB_DIFF3+                                | EIM_AD12<br>ALT5 GPIO3_IO12 |

| P71        | USB2_EN_OC#                               | Not connected                                                                                         | S72           | AFB_DIFF3-                                | EIM_AD13<br>ALT5 GPIO3_IO13 |

| P72        | PCIE_C_PRSNT#                             | Not connected                                                                                         | S73           | GND                                       | -                           |

| P73        | PCIE_B_PRSNT#                             | Not connected                                                                                         | S74           | AFB_DIFF4+                                | EIM_AD14<br>ALT5 GPIO3_IO14 |

| P74        | PCIE_A_PRSNT#                             | GPIO_18<br>ALT5 GPIO7_IO13                                                                            | S75           | AFB_DIFF4-                                | EIM_AD15<br>ALT5 GPIO3_IO15 |

|            | <key></key>                               | -                                                                                                     | ╢───          | <key></key>                               | -                           |

| P75        | PCIE_A_RST#                               | EIM_A19<br>ALT5 GPIO2_IO19                                                                            | S76           | PCIE_B_RST#                               | Not connected               |

| P76        | PCIE_C_CKREQ#                             | Not connected                                                                                         | S77           | PCIE_C_RST#                               | Not connected               |

| P77        | PCIE_B_CKREQ#                             | Not connected                                                                                         | S78           | PCIE_C_RX+                                | Not connected               |

| P78        | PCIE_A_CKREQ#                             | GPIO_0<br>ALT5 GPIO1_IO00                                                                             | S79           | PCIE_C_RX-                                | Not connected               |

| P79        | GND                                       | -                                                                                                     | S80           | GND                                       | -                           |

| TOP pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor         | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                 |

|---------|-------------------------------------------|-----------------------------------|---------------|-------------------------------------------|-------------------------------------------|

| P80     | PCIE_C_REFCK+                             | Not connected                     | S81           | PCIE_C_TX+                                | Not connected                             |

| P81     | PCIE_C_REFCK-                             | Not connected                     | S82           | PCIE_C_TX-                                | Not connected                             |

| P82     | GND                                       | -                                 | S83           | GND                                       | -                                         |

| P83     | PCIE_A_REFCK+                             | CLK1_P                            | S84           | PCIE_B_REFCK+                             | Not connected                             |

| P84     | PCIE_A_REFCK-                             | CLK1_N                            | S85           | PCIE_B_REFCK-                             | Not connected                             |

| P85     | GND                                       | -                                 | S86           | GND                                       |                                           |

| P86     | PCIE_A_RX+                                | PCIE_RXP                          | S87           | PCIE_B_RX+                                | Not connected                             |

| P87     | PCIE_A_RX-                                | PCIE_RXM                          | S88           | PCIE_B_RX-                                | Not connected                             |

| P88     | GND                                       | -                                 | S89           | GND                                       | -                                         |

| P89     | PCIE_A_TX+                                | PCIE_TXP                          | S90           | PCIE_B_TX+                                | Not connected                             |

| P90     | PCIE_A_TX-                                | PCIE_TXM                          | S91           | PCIE_B_TX-                                | Not connected                             |

| P91     | GND                                       | -                                 | S92           | GND                                       | -                                         |

| P92     | HDMI_D2+                                  | HDMI_D2P                          | S93           | LCD_D0                                    | DISP0_DAT0<br>ALT0/1 IPU1/2_DISP0_DATA00  |

| P93     | HDMI_D2-                                  | HDMI_D2M                          | S94           | LCD_D1                                    | DISP0_DAT1<br>ALT0/1 IPU1/2_DISP0_DATA01  |

| P94     | GND                                       | -                                 | S95           | LCD_D2                                    | DISP0_DAT2<br>ALT0/1 IPU1/2_DISP0_DATA02  |

| P95     | HDMI_D1+                                  | HDMI_D1P                          | S96           | LCD_D3                                    | DISP0_DAT3<br>ALT0/1 IPU1/2_DISP0_DATA03  |

| P96     | HDMI_D1-                                  | HDMI_D1M                          | S97           | LCD_D4                                    | DISP0_DAT4<br>ALT0/1 IPU1/2_DISP0_DATA04  |

| P97     | GND                                       | -                                 | S98           | LCD_D5                                    | DISP0_DAT5<br>ALT0/1 IPU1/2_DISP0_DATA05  |

| P98     | HDMI_D0+                                  | HDMI_D0P                          | S99           | LCD_D6                                    | DISP0_DAT6<br>ALT0/1 IPU1/2_DISP0_DATA06  |

| P99     | HDMI_D0-                                  | HDMI_D0M                          | S100          | LCD_D7                                    | DISP0_DAT7<br>ALT0/1 IPU1/2_DISP0_DATA07  |

| P100    | GND                                       | -                                 | S101          | GND                                       | -                                         |

| P101    | HDMI_CK+                                  | HDMI_CLKP                         | S102          | LCD_D8                                    | DISP0_DAT8<br>ALT0/1 IPU1/2_DISP0_DATA08  |

| P102    | HDMI_CK-                                  | HDMI_CLKM                         | S103          | LCD_D9                                    | DISP0_DAT9<br>ALT0/1 IPU1/2_DISP0_DATA09  |

| P103    | GND                                       | -                                 | S104          | LCD_D10                                   | DISP0_DAT10<br>ALT0/1 IPU1/2_DISP0_DATA10 |

| P104    | HDMI_HPD                                  | HDMI_HPD                          | S105          | LCD_D11                                   | DISP0_DAT11<br>ALT0/1 IPU1/2_DISP0_DATA11 |

| P105    | HDMI_CTRL_CK                              | KEY_COL3<br>ALT4 I2C2_SCL         | S106          | LCD_D12                                   | DISP0_DAT12<br>ALT0/1 IPU1/2_DISP0_DATA12 |

| P106    | HDMI_CTRL_DAT                             | KEY_ROW3<br>ALT4 I2C2_SDA         | S107          | LCD_D13                                   | DISP0_DAT13<br>ALT0/1 IPU1/2_DISP0_DATA13 |

| P107    | HDMI_CEC                                  | KEY_ROW2<br>ALT6 HDMI_TX_CEC_LINE | S108          | LCD_D14                                   | DISP0_DAT14<br>ALT0/1 IPU1/2_DISP0_DATA14 |

| P108    | GPIO0/CAM0_PWR#                           | NANDF_WP<br>ALT5 GPIO6_IO09       | S109          | LCD_D15                                   | DISP0_DAT15<br>ALT0/1 IPU1/2_DISP0_DATA15 |

| P109    | GPIO1/CAM1_PWR#                           | NANDF_RB0<br>ALT5 GPIO6_IO10      | S110          | GND                                       | -                                         |

| P110    | GPIO2/CAM0_RST#                           | NANDF_D0<br>ALT5 GPIO2_IO00       | S111          | LCD_D16                                   | DISP0_DAT16<br>ALT0/1 IPU1/2_DISP0_DATA16 |

| P111    | GPIO3/CAM1_RST#                           | NANDF_D1<br>ALT5 GPIO2_IO01       | S112          | LCD_D17                                   | DISP0_DAT17<br>ALT0/1 IPU1/2_DISP0_DATA17 |

| TOP pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                                                                   | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                  |

|---------|-------------------------------------------|---------------------------------------------------------------------------------------------|---------------|-------------------------------------------|--------------------------------------------|

| P112    | GPIO4/HDA_RST#                            | NANDF_D2<br>ALT5 GPIO2_IO02                                                                 | S113          | LCD_D18                                   | DISP0_DAT18<br>ALT0/1 IPU1/2_DISP0_DATA18  |

| P113    | GPIO5/PWM_OUT                             | SD1_DAT2<br>ALT3 PWM2_OUT                                                                   | S114          | LCD_D19                                   | DISP0_DAT19<br>ALT0/1 IPU1/2_DISP0_DATA19  |

| P114    | GPIO6/TACHIN                              | SD1_CLK<br>ALT3 GPT_CLKIN<br>SD1_DAT0<br>ALT3 GPT_CAPTURE1<br>SD1_DAT1<br>ALT3 GPT_CAPTURE2 | S115          | LCD_D20                                   | DISP0_DAT20<br>ALT0/1 IPU1/2_DISP0_DATA20  |

| P115    | GPIO7/PCAM_FLD                            | NANDF_D3<br>ALT5 GPIO2_IO03                                                                 | S116          | LCD_D21                                   | DISP0_DAT21<br>ALT0/1 IPU1/2_DISP0_DATA21  |

| P116    | GPIO8/CAN0_ERR#                           | NANDF_D4<br>ALT5 GPIO2_IO04                                                                 | S117          | LCD_D22                                   | DISP0_DAT22<br>ALT0/1 IPU1/2_DISP0_DATA22  |

| P117    | GPIO9/CAN1_ERR#                           | NANDF_D5<br>ALT5 GPIO2_IO05                                                                 | S118          | LCD_D23                                   | DISP0_DAT23<br>ALT0/1 IPU1/2_DISP0_DATA23  |

| P118    | GPIO10                                    | NANDF_D6<br>ALT5 GPIO2_IO06                                                                 | S119          | GND                                       | -                                          |

| P119    | GPIO11                                    | NANDF_D7<br>ALT5 GPIO2_IO07                                                                 | S120          | LCD_DE                                    | DI0_PIN15<br>ALT0/1 IPU1/2_DI0_PIN15       |

| P120    | GND                                       | -                                                                                           | S121          | LCD_VS                                    | DI0_PIN3<br>ALT0/1 IPU1/2_DI0_PIN3         |

| P121    | I2C_PM_CK                                 | CSI0_DAT9<br>ALT4 I2C1_SCL                                                                  | S122          | LCD_HS                                    | DI0_PIN2<br>ALT0/1 IPU1/2_DI0_PIN2         |

| P122    | I2C_PM_DAT                                | CSI0_DAT8<br>ALT4 I2C1_SDA                                                                  | S123          | LCD_PCK                                   | DI0_DISP_CLK<br>ALT0/1 IPU1/2_DI0_DISP_CLK |

| P123    | BOOT_SEL0#                                | CPLD                                                                                        | S124          | GND                                       | -                                          |

| P124    | BOOT_SEL1#                                | CPLD                                                                                        | S125          | LVDS0+                                    | LVDS0_TX0_P                                |

| P125    | BOOT_SEL2#                                | CPLD                                                                                        | S126          | LVDS0-                                    | LVDS0_TX0_N                                |

| P126    | RESET_OUT#                                | EIM_A18<br>ALT5 GPIO2_IO20                                                                  | S127          | LCD_BKLT_EN                               | EIM_A21<br>ALT5 GPIO2_IO17                 |

| P127    | RESET_IN#                                 | POR#                                                                                        | S128          | LVDS1+                                    | LVDS0_TX1_P                                |

| P128    | POWER_BTN#                                | ONOFF                                                                                       | S129          | LVDS1-                                    | LVDS0_TX1_N                                |

| P129    | SER0_TX                                   | EIM_D24<br>ALT2 UART3_TX_DATA                                                               | S130          | GND                                       | -                                          |

| P130    | SER0_RX                                   | EIM_D25<br>ALT2 UART3_RX_DATA                                                               | S131          | LVDS2+                                    | LVDS0_TX2_P                                |

| P131    | SER0_RTS#                                 | EIM_D23<br>ALT2 UART3_CTS_B                                                                 | S132          | LVDS2-                                    | LVDS0_TX2_N                                |

| P132    | SER0_CTS#                                 | EIM_EB3<br>ALT2 UART3_RTS_B                                                                 | S133          | LCD_VDD_EN                                | EIM_A20<br>ALT5 GPIO2_IO18                 |

| P133    | GND                                       | -                                                                                           | S134          | LVDS_CK+                                  | LVDS0_CLK_P                                |

| P134    | SER1_TX                                   | CSI0_DAT10<br>ALT3 UART3_TX_DATA                                                            | S135          | LVDS_CK-                                  | LVDS0_CLK_N                                |

| P135    | SER1_RX                                   | CSI0_DAT11<br>ALT3 UART3_RX_DATA                                                            | S136          | GND                                       | -                                          |

| P136    | SER2_TX                                   | EIM_D26<br>ALT4 UART2_TX_DATA                                                               | S137          | LVDS3+                                    | LVDS0_TX3_P                                |

| P137    | SER2_RX                                   | EIM_D27<br>ALT4 UART2_RX_DATA                                                               | S138          | LVDS3+                                    | LVDS0_TX3_N                                |

| P138    | SER2_RTS#                                 | EIM_D28<br>ALT4 UART2_CTS_B                                                                 | S139          | I2C_LCD_CK                                | GPIO_3<br>ALT2 I2C3_SCL                    |

| P139    | SER2_CTS#                                 | EIM_D29<br>ALT4 UART2_RTS_B                                                                 | S140          | I2C_LCD_DAT                               | GPIO_6<br>ALT2 I2C3_SDA                    |

| TOP pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                      | BOTTOM<br>pin | Purpose of the<br>SMARC connector<br>pins | Output of i.MX6 processor                           |

|---------|-------------------------------------------|------------------------------------------------|---------------|-------------------------------------------|-----------------------------------------------------|

| P140    | SER3_TX                                   | Not connected                                  | S141          | LCD_BKLT_PWM                              | SD1_DAT3                                            |

| P141    | SER3_RX                                   | Not connected                                  | S142          | LCD_DUAL_PCK                              | ALT3 PWM1_OUT<br>DI0_PIN4<br>ALT0/1 IPU1/2_DI0_PIN4 |

| P142    | GND                                       | -                                              | S143          | GND                                       | -                                                   |

| P143    | CAN0_TX                                   | GPIO_7<br>ALT3 FLEXCAN1_TX <mark>(3.3V)</mark> | S144          | RSVD/EDP_HPD                              | Not connected                                       |

| P144    | CAN0_RX                                   | GPIO_8<br>ALT3 FLEXCAN1_RX (3.3V)              | S145          | WDT_TIME_OUT#                             | GPIO_9<br>ALT1_WDOG1_B                              |

| P145    | CAN1_TX                                   | KEY_COL4<br>ALT0 FLEXCAN2_TX (3.3V)            | S146          | PCIE_WAKE#                                | KEY_COL2<br>ALT5 GPIO4_IO10                         |

| P146    | CAN1_RX                                   | KEY_ROW4<br>ALT0 FLEXCAN2_RX (3.3V)            | S147          | VDD_RTC                                   | -                                                   |

| P147    | VDD_IN                                    | -                                              | S148          | LID#                                      | EIM_D20 ALT5<br>GPIO                                |

| P148    | VDD_IN                                    | -                                              | S149          | SLEEP#                                    | EIM_A25 ALT5<br>GPIO                                |

| P149    | VDD_IN                                    | -                                              | S150          | VIN_PWR_BAD#                              | -                                                   |

| P150    | VDD_IN                                    | -                                              | S151          | CHARGING#                                 | NANDF_CS3<br>ALT5 GPIO6_IO16                        |

| P151    | VDD_IN                                    | -                                              | S152          | CHARGER_PRSNT#                            | NANDF_CLE<br>ALT5 GPIO6_IO17                        |

| P152    | VDD_IN                                    | -                                              | S153          | CARRIER_STBY#                             | EIM_A17<br>ALT5 GPIO2_IO21                          |

| P153    | VDD_IN                                    | -                                              | S154          | CARRIER_PON                               | EIM_A16<br>ALT5 GPIO2_IO22                          |

| P154    | VDD_IN                                    | -                                              | S155          | FORCE_RECOV#                              | NANDF_CS1<br>ALT5 GPIO6_IO14                        |

| P155    | VDD_IN                                    | -                                              | S156          | BATLOW#                                   | NANDF_CS2<br>ALT5 GPIO6_IO15                        |

| P156    | VDD_IN                                    | -                                              | S157          | TEST#                                     | NANDF_CS0<br>ALT5 GPIO6_IO11                        |

|         |                                           | -                                              | S158          | VDD_IO_SEL_D#                             | GND                                                 |

Notes to the Table 1.1:

- The differences from the SMARC specification are highlighted in red (signal P43 (SPI0\_CS0 #) not connected; signals P143 - P146 (CAN0 / 1) - 3.3V).

– In accordance with the SMARC specification, version 1.1, VDD\_IO\_SEL\_D# signal (pin S158 of the SMARC connector) is no longer designed for (compared to the SMARC 1.0 version) indication of the voltage level VDD\_IO; in CPC1001 VDD\_IO=1,8 V for all the signals, except for those, for which the voltage level of 3.3 V (auxiliary signals of SDIO, USB, PCIE, SATA and GBE interfaces), as well as CAN0/1 signals, are set by the specification.

#### 1.6.3 Compliance of the SMARC interfaces and interface controllers of i.MX6

For reference, Table 1.2 shows the compliance of the SMARC interfaces and interface controllers of the i.MX6 processor in CPC1001.

| SMARC    | i.MX6    | Devices on CPC1001                                               |

|----------|----------|------------------------------------------------------------------|

| I2C_HDMI | I2C2     | -                                                                |

| I2C_LCD  | I2C3     | -                                                                |

| I2C_CAM  | I2C2     | RTC PCF8523TK, address 0xD0, (only in version CPC1001-01)        |

| I2C_PM   | I2C1     | EEPROM AT24C32D, address 0xA0                                    |

| I2C_GP   | I2C3     | -                                                                |

| SPI0     | ECSPI1   | EEPROM AT45DB321E,<br>EIM_EB2 ALT1 ECSPI1_SS0 or ALT5 GPIO2_IO30 |

| SPI1     | ECSPI2   | -                                                                |

| I2S0     | AUD3     | -                                                                |

| I2S1     | AUD5     | -                                                                |

| SER0     | UART3    | -                                                                |

| SER1     | UART1    | -                                                                |

| SER2     | UART2    | -                                                                |

| CAN0     | FLEXCAN1 | -                                                                |

| CAN1     | FLEXCAN2 | -                                                                |

Table 1.2 – Compliance of the SMARC interfaces and i.MX6 processor

#### 1.6.4 Arrangement of 16-bit parallel bus

An additional feature of the CPC1001 module, which may be of interest within a number of applications, is the possibility of organizing a high-performance 16-bit parallel bus with a multiplexed address based on the EIM interface controller of the i.MX6 processor. The bus uses the signals listed in Table 1.3.

| Table 1.3 – Signals of parallel bus |                           |  |  |  |

|-------------------------------------|---------------------------|--|--|--|

| SMARC                               | Parallel bus              |  |  |  |

| SPI1_CK                             | EIM_CS0, ALT0 EIM_CS0_B   |  |  |  |

| SPI1_DO                             | EIM_CS1, ALT0 EIM_CS1_B   |  |  |  |

| SPI1_DIN                            | EIM_OE, ALT0 EIM_OE_B     |  |  |  |

| SPI1_CS0#                           | EIM_RW, ALTO EIM_RW       |  |  |  |

| SPI1_CS1#                           | EIM_LBA, ALT0 EIM_LBA_B   |  |  |  |

| AFB0_OUT                            | EIM_BCLK, ALTO EIM_BCLK   |  |  |  |

| AFB1_OUT                            | EIM_WAIT, ALTO EIM_WAIT_B |  |  |  |

| AFB2_OUT                            | EIM_EB0, ALT0 EIM_EB0_B   |  |  |  |

| AFB3_IN                             | EIM_EB1, ALT0 EIM_EB1_B   |  |  |  |

| AFB4_IN                             | EIM_AD00, ALT0 EIM_AD00   |  |  |  |

| AFB5_IN                             | EIM_AD01, ALT0 EIM_AD01   |  |  |  |

| AFB6_PTIO                           | EIM_AD02, ALT0 EIM_AD02   |  |  |  |

| AFB7_PTIO                           | EIM_AD03, ALT0 EIM_AD03   |  |  |  |

| AFB8_PTIO                           | EIM_AD04, ALT0 EIM_AD04   |  |  |  |

| AFB9_PTIO                           | EIM_AD05, ALT0 EIM_AD05   |  |  |  |

| AFB_DIFF0+                          | EIM_AD06, ALT0 EIM_AD06   |  |  |  |

| AFB_DIFF0-                          | EIM_AD07, ALT0 EIM_AD07   |  |  |  |

| AFB_DIFF1+                          | EIM_AD08, ALT0 EIM_AD08   |  |  |  |

| AFB_DIFF1-                          | EIM_AD09, ALT0 EIM_AD09   |  |  |  |

| AFB_DIFF2+                          | EIM_AD10, ALT0 EIM_AD10   |  |  |  |

| AFB_DIFF2-                          | EIM_AD11, ALT0 EIM_AD11   |  |  |  |

| AFB_DIFF3+                          | EIM_AD12, ALT0 EIM_AD12   |  |  |  |

| AFB_DIFF3-                          | EIM_AD13, ALT0 EIM_AD13   |  |  |  |

| AFB_DIFF4+                          | EIM_AD14, ALT0 EIM_AD14   |  |  |  |

| AFB_DIFF4-                          | EIM_AD15, ALT0 EIM_AD15   |  |  |  |

| Table 1.3 – | Signals of  | parallel bus |

|-------------|-------------|--------------|

|             | orginalo or | paranor buo  |

# 1.7 Delivery checklist

CPC1001 is supplied as follows:

- CPC1001 module in an antistatic bag;

- Packaging.

## 1.8 Packaging

#### 1.8.1 Size of the consumer container and weight of the packaged product

Upon delivery, CPC1001 is packed in individual consumer packaging (cardboard box) with dimensions  $155 \times 140 \times 45$  mm. The device's weight in package: - no more than 0.2 kg.

#### 1.8.2 Labelling of consumer containers

Consumer packaging is labelled by means of an individual identifier (sticker).

The container sticker should have the following information:

- Product designation according to the ordering information (subparagraph 1.5);

- Product version;

- Product serial number;

- Manufacturer's trademark;

- Barcode.

#### 1.8.3 Order of packing

Retain the original packaging for storing the product or for shipping in case of a warranty event. If it is necessary to transport or store the product, pack it in the same way as it was packed at the time of receipt (product in an antistatic bag). The box should be sealed to maintain its integrity during transportation.

# 2 Intended use

## 2.1 Operating limitations

Operation of CPC1001 is not allowed under the influence of external factors that do not comply with paragraph 1.2.11.

Fastwel Group does not recommend long-term operation of the products near the limit values of the operating temperature range. The nature of these processes is common for reducing the mean time between failures due to the increased likehood of failure. Long-term operation of the product within the operating temperature range is not limited.

Any exposure to electromagnetic interference that does not comply with paragraph 1.2.12, should be avoided.

It is not allowed to send signals to the contacts of the SMARC connector (see Fig.1.2), which parameters do not meet the requirements of the I/O interfaces (paragraph 1.6.2, Table 1.1). Power supply that does not meet the requirements of paragraph 1.2.10 is not allowed.

# 2.2 Safety requirements

This Fastwel product has been developed and tested in accordance with electrical safety requirements. It is designed for long-term and fail-safe operation. The service life of the device can be significantly reduced due to improper handling. Therefore, in the interests of your safety and to ensure the proper operation of the product, you should adhere to the requirements and recommendations given in this User Manual.

For maintaining the warranty, no alterations or modifications should be performed on the product. Any changes and improvements unauthorized by Fastwel Group will void the warranty.

The products should not be exposed to mechanical shocks and drops. Do not leave the module in the non-operating position without protective packaging. Please remember that any mechanical damage makes the product ineligible for warranty service.

Installing CPC1001 on a carrier board is allowed only when the power is off. There is a risk of electric shock during installation and maintenance of the products, so always disconnect the power supply during any preliminary works and preparations.

The product contains components sensitive to static electricity. Observe the following precautions to avoid damaging the module:

– You should remove the static charge from your clothes before touching the module. The best way to do so is by touching any metal part of the system enclosure.

- Do not touch electronic components or connector pins.

- If possible, always work with the module in workplaces protected against static electricity.

#### 2.3 Information on the types of hazardous effects

In terms of its design, the device is safe for human life and health when used in accordance with this User Manual and contains no public health hazards (paragraph 1.2.12).

#### 2.4 Heat removal

Reliable operation of the CPC1001 module requires a properly designed heat removal system, with due consideration to the following factors:

- the heat removal of the module largely depends on the executable end-user and system software and, therefore, must be estimated for each specific application (the reference information is given in paragraph 1.2.10);

the heat-dissipation plate of the CPC1001-01 module, without an additionally installed heatsink (and fan), in general, would be insufficient for proper heat dissipation;

– Operating system, depending on its settings, is capable of monitoring the readings of the temperature sensor<sup>2</sup> built into the processor module during operation and can respond to exceeding of configurable thresholds<sup>3</sup> as follows:

respond by decreasing in the frequency of computing cores and processor's graphics controller if the first threshold is exceeded (recommended value: +85 °C);

respond by an immediate shutdown if the second threshold is exceeded (recommended value: +105 °C);

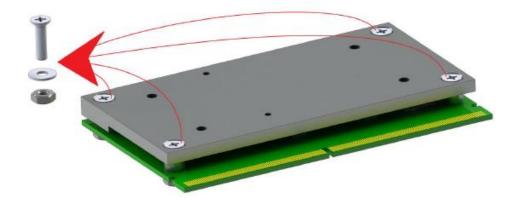

For long-term failsafe operation, the temperature of the CPU module, measured on its enclosure or on the heat-distribution plate (the recommended temperature measurement zone is shown in Fig. 2.2), should not exceed +95 °C under all permissive external conditions.

If the natural heat dissipation is insufficient, a heatsink should be used (it is recommended to install the heatsink using a thermal paste) and, if necessary, a fan should also be used, the requirements for which are determined based on the operating features, with due consideration to the information given above. If the CPC1001-01 module is used, the heatsink is fastened to the heat-distribution plate with four M3 screws in the corresponding holes (see Fig. 2.2).

The maximum permissible depth of securing the screws into the M3 holes of the heatsink of the CPC1001-01 module (Fig. 2.2) is 4 mm.

#### 2.5 Installation of CPC1001

The carrier board for the CPC1001 must comply with the SMARC specification version 1.1 subject to the compatibility restrictions specified in the *Note* given in subparagraph 1.6.2. Information on mating connectors of the carrier board and standoffs recommended to installation of CPC1001 is given in the table 2.1

$^{2}\,\text{Measurement}$  error may be up to ±6 °C.

<sup>&</sup>lt;sup>3</sup> Thresholding method depends on the operating system used.

| Stack height,<br>mm | Connector<br>(Foxconn) | Standoffs<br>(Würth Elektronik) | Note                                                                                                                                                                                                                                                             |

|---------------------|------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.5                 | AS0B826-S43*           | 9774015151                      | If you need to use components with a stack height of<br>less than 2.7 mm on the carrier board, you may need a<br>recess for the CPC1001 connector of the Molex type<br>50003340200 (used for technological purposes at<br>manufacturer facilities), see Fig. 2.2 |

| 2.7                 | AS0B826-S55*           | 9774027151                      |                                                                                                                                                                                                                                                                  |

| 5.0                 | AS0B826-S78*           | 9774050151                      |                                                                                                                                                                                                                                                                  |

#### Table 2.1 – Recommended components for CPC1001 installation to the carrier-board

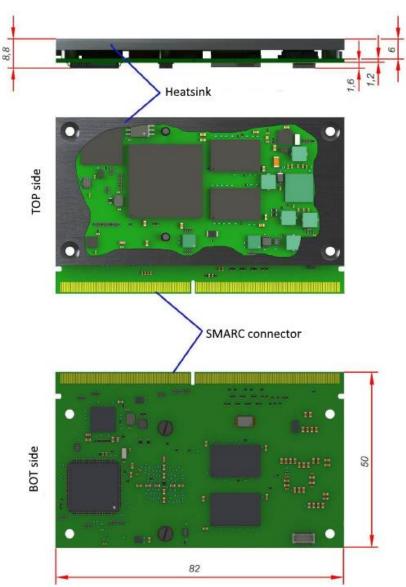

Immediately prior to installing the CPC1001-01 module on the carrier board, remove the **shipping** screws and fasteners (see Fig. 2.1):

- Countersunk screw M2.5x10 4 pcs.

- Nut M2.5 4 pcs.

- Washer 4 pcs.

Fig. 2.1 – Removal of the shipping screws on CPC1001-01

Installing CPC1001 on a carrier board is allowed only when the power is off. Failure to comply with the above requirements may result in damages to the CPC1001 module and the carrier board.

The SMARC connector of the CPC1001 module should be carefully inserted into the mating connector of the carrier board (if necessary, pre-install the heatsink and the fan on CPC1001 (subparagraph 2.4)).

When installed on the carrier board, the CPC1001 module is fastened on the standoffs using 4 x M2.5 screws through the  $\emptyset$ 2.9 mm holes (see Fig. 2.2).

Fig. 2.2 – Mounting dimensions of CPC1001-01

# 2.6 Selection of OS boot source

One of the 8 possible sources of OS boot is selected by setting static levels at the inputs BOOT\_SEL [2 ... 0]# (pins P125 ... 123 of the SMARC connector) in accordance with table. 2.2.

| BOOT_SEL[20]# | OS boot source                                                                              |  |  |  |

|---------------|---------------------------------------------------------------------------------------------|--|--|--|

| 000           | SATA on the carrier board                                                                   |  |  |  |

| 001           | SD card on the carrier board (µSDHC2)                                                       |  |  |  |

| 010           | eMMC Flash on the carrier board (µSDHC3)                                                    |  |  |  |

| 011           | SPI Flash on the carrier board (SPI0_CS1#)<br>EIM_D19 ALT1 ECSPI1_SS1 or ALT5<br>GPIO3_IO19 |  |  |  |

| 100           | MMC-card on the carrier board (µSDHC2)                                                      |  |  |  |

| 101           | Serial Boot (USB_OTG)                                                                       |  |  |  |

| 110           | Onboard eMMC Flash (µSDHC4)                                                                 |  |  |  |

| 111           | Onboard SPI Flash (SPI0_CS0#)<br>EIM_EB2 ALT1 ECSPI1_SS0 or ALT5<br>GPI02_IO30              |  |  |  |

| Table | 2.2 -   | Boot | sources | of         | CPC1001  |

|-------|---------|------|---------|------------|----------|

| TUDIC | <u></u> | DOOL | 3001003 | <b>U</b> 1 | 01 01001 |

BOOT\_SEL [2... 0] # signals in CPC1001 have a pull-up, which ensures a high signal level ("1") where there are no external connections. To set the low level of signal ("0"), the relevant circuit on the carrier board must be grounded. The state of the BOOT\_SEL [2 ... 0]# signals is considered only at the time of the end of the CPC1001 hardware reset signal, therefore the selected source will be saved during any further reboots initiated by the operating system or when the watchdog timer is triggered.

For rebooting from the sources located on the carrier board, the corresponding devices must be supplied with power by the time the boot starts. That is, it should not depend on the CARRIER\_PWR\_ON and CARRIER\_STBY# signals. The SDIO\_PWR\_EN signal, however, *can* be used to control power to the SD card on the carrier board.

### 2.7 Power up and down

The power is fed via the SMARC connector (subparagraph 1.6.2). Requirements to the supply voltages of CPC1001 are given in Table 2.3.